## TUTORIAL

# **CADENCE DESIGN**

# ENVIRONMENT

Ivan Padilla Cantoya

ivan.padilla@academicos.udg.mx

Departamento de Electrónica Universidad de Guadalajara

January 2018

#### CONTENTS

| 1. INTRODUCTION                                   | 4   |

|---------------------------------------------------|-----|

| 2. ANALOG IC DESIGN FLOW AND REQUIRED TOOLS       | 4   |

| 3. SETTING YOUR UNIX ENVIRONMENT                  | 5   |

| 4. RUNNING CADENCE                                | 6   |

| 5. ANALOG DESIGN WITH CADENCE DESIGN FRAMEWORK    | II8 |

| 5.1. Library Creation and Selection of Technology | 8   |

| 5.2. Schematic Entry with Composer                | 9   |

| 5.2.1. Symbol Creation                            | 11  |

| 5.3. Simulation                                   | 13  |

| 5.3.1. Setting simulator                          | 14  |

| 5.3.2. Setting models                             | 14  |

| 5.3.3. Setting design variables                   | 14  |

| 5.3.4. Selecting the analysis                     | 15  |

| 5.3.5. Running the simulation                     | 15  |

| 5.3.6. Plotting the simulation results            | 15  |

#### **1. INTRODUCTION**

This manual is intended to introduce microelectronic designers to the Cadence Design Environment, and to describe all the steps necessary for running the Cadence tools at the Departamento de Electrónica, Sistemas e Informática. Cadence is an Electronic Design Automation (EDA) environment that allows integrating in a single framework different applications and tools (both proprietary and from other vendors), allowing to support all the stages of IC design and verification from a single environment. These tools are completely general, supporting different fabrication technologies. When a particular technology is selected, a set of configuration and technology-related files are employed for customizing the Cadence environment. This set of files is commonly referred as a *design kit*.

It is not the objective of this manual to provide an in-depth coverage of all the applications and tools available in Cadence. Instead, a detailed introduction to those required for an analog designer, from the conception of the circuit to its physical implementation, is provided. References to other manuals and information sources with a deeper treatment of these and other Cadence tools are also provided.

#### 2. ANALOG IC DESIGN FLOW AND REQUIRED TOOLS

Fig. 1 shows the basic design flow of an analog IC design, together with the Cadence tools required in each step. First, a schematic view of the circuit is created using the Cadence *Composer Schematic Editor*. Alternatively, a text netlist input can be employed. Then, the circuit is simulated using the Cadence *Affirma* analog simulation environment. Different simulators can be employed, some sold with the Cadence software (e.g., Spectre) some from other vendors (e.g., HSPICE) if they are installed and licensed. Once circuit specifications are fulfilled in simulation, the circuit layout is created using the *Virtuoso Layout Editor*. The resulting layout must verify some geometric rules dependent on the technology (design rules). For enforcing it, a *Design Rule Check* (DRC) is performed. Optionally, some electrical errors (e.g. shorts) can also be detected using an *Electrical Rule Check* (ERC). Then, the layout should be compared to the circuit schematic to ensure that the intended functionality is implemented. This can be done with a *Layout Versus Schematic* (LVS) check. All these verification tools are included in the *Diva* software in Cadence (more powerful Cadence tools can also be available, like *Dracula*, or

*Assura* in deep submicron technologies). Finally, a netlist including all layout parasitics should be extracted, and a final simulation of this netlist should be made. This is called a *Post-Layout simulation*, and is performed with the same Cadence simulation tools. Once verified the layout functionality, the final layout is converted to a certain standard file format depending on the foundry (GDSII, CIF, etc.) using the Cadence conversion tools.

Figure 1. Analog IC design flow and Cadence tools involved

#### **<u>3. RUNNING CADENCE</u>**

The DESI department counts with two laboratories, F-101 and 102, which have 16 computers each, with the required software loaded and properly configured. Cadence can be run from the desktop, by double-clicking on the icon named Virtuoso NCSU. Thus, Cadence starts as shown in Fig. 1.

Also, you can run Cadence from your working directory (if already created) by typing: Bash-2.05a\$ *icfb.exe* or, equivalently: Bash-2.05a\$ *virtuoso*

Figure 1. Red Hat desktop, showing the Virtuoso NCSU icon which starts Cadence.

Afterwards, the Cadence main window (**Common Interface Window, CIW**) and the **Library Manager Window** are opened, both shown in Fig. 2.. From the CIW menus, all Cadence main tools, online help and options can be accessed. In the window area, all kind of messages (info, errors, warnings, etc) generated by the different Cadence tools appear. You can also introduce commands.

| Library Manager: WorkArea: /home/usuario/NCSU File Edit View Design Manager                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                          |      | Help |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------|------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                          |      | Timb |

| Show Categories Show Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                          |      |      |

| Library                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Cell                                                                                                     | View |      |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                                                                        | 1    |      |

| 100515_Layout_Tet<br>10051_Aniog Parts<br>1005_Aniog Parts<br>1005_Aniog Parts<br>1005_TetLis_ani6<br>1005_TetLis_ani6<br>1005_TetLis_ani6<br>1005_TetLis_tax023<br>1005_TetLis_tax023<br>1005_TetLis_tax023<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax03<br>1005_TetLis_tax |                                                                                                          |      |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                          |      |      |

| Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                          |      |      |

| Cell filer set to ""<br>Yuew filer set to ""<br>Log file is "/heme/usuario/MESU/libHamager log                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | а.                                                                                                       |      |      |

| File Tool                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Log: /homme/usuario/CDS.log<br>15 Options<br>anisherv cot<br>appicol cot<br>ang NOSU_CDK customizations. | Help |      |

| <b>&amp; \$\$ \$</b> \$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | icfb - Log: /home/usuario                                                                                |      |      |

| <b>D</b> <sup>1</sup> <b>O</b> (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                          | 1 16 |      |

Figure 2. CIW window and Library Manager window.

All the entities in Cadence are managed using **libraries**, and each library contains **cells**. Each cell contains different design **views** (the structure is similar –and physically corresponds - to a directory (library) containing subdirectories (cells), each one containing files (views). Thus,

for instance, a certain circuit (e.g. an ADC) can be stored in a library, and such library can contain the different ADC blocks (comparators, registers, resistor strings, etc) stored as cells. Each block (cell) contains different views (schematic, layout, etc.). There are usually three types of libraries:

- A set of common Cadence libraries that come with the Cadence software (containing basic components, such as voltage and current sources, R, L, C, etc).

- Libraries that come with a certain design kit and that are related to a certain technology (e.g. transistors with a certain model attached, etc). In the NCSU design kit, some general Cadence libraries are customized and converted into design kit libraries.

- User libraries; where the user stores its designs. These designs employ components from the Cadence/design kit libraries.

All the libraries are managed from the Library Manager Window. It appears by default at Cadence start, and can be opened at any time by selecting *Tools>Library Manager...* from the CIW. Libraries with names starting by NCSU are design kit libraries, and contain basic components for building designs. In Fig. 3, they are:

- *NCSU\_Analog\_Parts*: contains all the required blocks for designing an analog schematic (sources, GND and VDD terminals, transistors, R, L, C, diodes, etc.)

- *NCSU\_Digital\_Parts*: similarly, it contains all parts required for digital design (logic gates, muxes, etc.)

- *NCSU\_Sheets\_8ths:* it contains informative sheet borders for the schematics, in different sheet sizes. Its use is optional, for design documentation.

- *NCSU\_TechLibAMI06:* it is a technology-specific library that is created when the user attaches this particular technology (AMI06) to a user library.

#### 5. ANALOG DESIGN WITH CADENCE DESIGN FRAMEWORK II

Now we are going to illustrate how to carry out the complete design flow shown in Fig. 1 using the Cadence tools. A simple inverter will be designed using the AMI  $0.5\mu m$  CMOS technology. However, the same procedures apply to complete chip designs.

#### 5.1. Library creation and selection of technology

It is recommended that you use a library to store related cell views; e.g., use a library to hold all the cell views for a single project (that can involve a complete chip design). In our example, we are going to create a new library for our design. From the CIW or from the Library Manager window,

- a) Select *File -> New -> Library*. A new window appears (see Fig. 3).

- b) Enter a library name, e.g., **example** and click *OK*.

- c) Enter the absolute path name if you want the library created somewhere else than the working directory.

- d) A new window will open as shown in Fig. 4, choose the **Attach to an existing techfile** option to link the new library to the proper technology.

- e) Choose your proper technology, see Fig. 5; for instance, for AMI 0.5μm in MOSIS, choose AMI 0.6u C5N.

NOTE: The NCSU Kit 1.6u and 0.6u AMI processes correspond to MOSIS' 1.5µ and 0.5µ. For consistency, the NCSU kit names its tech libs based on the drawn length of devices, so this sometimes runs afoul of MOSIS' naming scheme.

| Name     |                                 |  |

|----------|---------------------------------|--|

| Name     | pruebal                         |  |

| Director | Y                               |  |

|          |                                 |  |

|          |                                 |  |

|          |                                 |  |

|          |                                 |  |

|          |                                 |  |

| (hone (  | venerio (MCCIŤ                  |  |

| /home/   | usuario/NCSU <u></u>            |  |

|          | usuario/NCSU <u></u><br>Manager |  |

|          | Manager                         |  |

Figure 3. Create Library window.

Figure 4. Attach technology library window.

| <ul> <li>Attach Design Librar</li> </ul> | to Technology Fi | le 3             |

|------------------------------------------|------------------|------------------|

| OK Cancel Defa                           | ( (              | Help             |

| New Design Library                       | prueba1          |                  |

| Technology Library                       | NCSU             | _TechLib_ami06 _ |

Figure 5. Technology library window.

This will be the technology chosen for your design (that you will employ eventually for fabrication). Now all the designs made in this library are technology-dependent (i.e. the schematic MOS symbols have by default the model for this technology, the available layout layers correspond to this technology, etc.).

#### 5.2. Schematic Entry with Composer

#### 5.2.1. Transistor-level schematic

The traditional method for capturing (i.e. describing) your transistor-level or gate-level design is via the Composer schematic editor. Schematic editors provide simple, intuitive means to draw, place and connect individual components that make up your design. The resulting schematic drawing must accurately describe the main electrical properties of all components and their interconnections. Also included in the schematic are the power supply and ground connections, as well as all "pins" for the input and output signals of your circuit. This information is crucial for generating the corresponding netlist, which is used in later stages of the design. The generation of a complete circuit schematic is therefore the first important step of

the former design flow. Usually, some properties of the components (e.g. transistor dimensions) and/or the interconnections between the devices are subsequently modified as a result of iterative optimization steps. These later modifications and improvements on the circuit structure must also be accurately reflected in the most current version of the corresponding schematic.

Now you are going to create the schematic of the inverter. From the CIW or from the Library Manager window:

- a) Select the library name that you just created, e.g., **example**.

- b) Select *File -> New -> Cellview*

- c) Enter a cell name, for instance, inverter

- d) Choose **Composer Schematic** as the **Tool**. Important: View name should be *schematic*.

- e) Click OK.

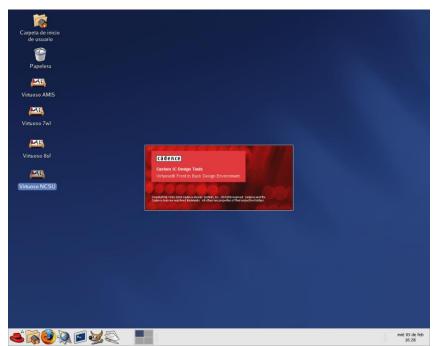

An empty blank Composer - schematic window should open. In this window you will create the schematic of the inverter. To create it, you can employ the window top menus or left icons (or also short keys), described in Fig. 6. This multiple access to actions is common to all the Cadence tools. A detailed information concerning the use of the schematic editor can be obtained by selecting **Help** from this window. Basically, you can:

• Create components: by selecting the **Instance** icon and browsing in the pop-up window through the different libraries. Most components (transistors, R, L, C, sources, rail terminals, etc.) are in the NCSU\_Analog\_Parts library. When an instance of a certain component is created (e.g. transistor, R, C, etc.) a window appears where you can select the properties of this element as in Fig. 7. Note that for transistors, the model is automatically set according to the technology you have selected, and that some parameters (drain and source area and perimeter, etc) are automatically calculated. NOTE: There are three-terminal (nmos, pmos) and four-terminal (nmos4, pmos4) MOS devices available. The three-terminal devices have a hidden fourth (bulk) terminal, which is connected by default to "gnd!" for nmos and "vdd!" for pmos. This means that you need to have nets named "vdd!"and "gnd!" somewhere in your schematic. (The easiest way to do this is to drop in the vdd and gnd pins from NCSU\_Analog\_Parts->Supply\_Nets.) If you don't have these nets in your schematic somewhere, you'll get complaints about unknown nets either in the netlister or in LVS. (You can also change the bulk node in the three-terminal device if you want to. Just select the device in the schematic, and bring up the "Edit Object Properties" form (Edit->Object- >Properties...). Change the "Bulk node connection" field to whichever net you want.

Figure 6. Schematic window.

|                                  | Library Manager: WorkArea:                  | /home/usuario/NCSI      | _ 1                                                               | = ×              |

|----------------------------------|---------------------------------------------|-------------------------|-------------------------------------------------------------------|------------------|

| EU                               |                                             |                         |                                                                   | elp              |

|                                  | Show Categories 🔄 Show                      | w Files                 |                                                                   |                  |

|                                  | ibrary                                      |                         | Cell                                                              |                  |

|                                  | uebal 💙 Virtuo so®                          |                         | oruebal circ1 schematic –                                         | ×                |

| -                                | SIS Layout T                                | nce Sel: 0              |                                                                   | 2                |

| NCS                              |                                             | n Window Edit Add       | Check Sheet Options Migrate NCSU He                               | lp i             |

| NCS                              | SU_TechLib_a                                |                         |                                                                   |                  |

| NC                               | ♥ Library Browser - Add I                   | nstance                 | - • ×                                                             |                  |

| NC<br>NC                         | 🔽 Show Categories                           |                         |                                                                   |                  |

| NC                               | Library                                     | Category                | Cell View                                                         |                  |

| NC<br>NC                         | NCSU_Analog_Parts                           | N_Transistors           | janos4 jsymbol                                                    |                  |

| av                               | MOSIS_Layout_Test                           | Everything              | N_Transistors_Index auCdl                                         |                  |

| ba                               | NCSU_Analog_Parts<br>NCSU_Digital_Parts     | Uncategorize            | nbsin auLvs<br>nbsin4 cdsSpice                                    |                  |

| pr                               | NCSU_TechLib_ani06<br>NCSU_TechLib_ani16    | CONTENTS                | njfet hspiceS mas ivpcell                                         |                  |

|                                  | NCSU TechLib hp06                           | Current_Sour            | nmes4 spectre                                                     |                  |

|                                  | NCSU_TechLib_tsnc02<br>NCSU TechLib tsnc02d | Diodes                  | rmos spectreS symbol                                              |                  |

|                                  | NCSU TechLib_tsnc03<br>NCSU TechLib_tsnc03d | H_Spice_Only            | nmos4_hv symbol.publication                                       |                  |

|                                  | NCSU_TechLib_tsmc04_4M                      | Microvave Pa            | npn                                                               |                  |

|                                  | avTech<br>basic                             | Misc_Parts              | usernpn                                                           |                  |

|                                  | cdsDefTechLib                               | N_Transistor            |                                                                   |                  |

| - N                              | pruebal                                     | P_Transistor:           |                                                                   |                  |

| Ce                               |                                             | 🗄 Parasitic_De          | · · · · · · · · · · · · · · · · · · ·                             |                  |

| Vi<br>Lo                         |                                             | B R_L_C                 | V Add Instance                                                    |                  |

| De                               |                                             | Spectre_Only            | Hide Cancel Defaults Help                                         |                  |

| Ce<br>Vi<br>Lc<br>De<br>De<br>Cr |                                             | Supply_Nets             | Library NCSU_Analog_Parts Browse                                  |                  |

| De<br>Cr                         |                                             | Voltage_Sour            | Cell nnos4                                                        |                  |

| 1                                |                                             | despice_Only            |                                                                   |                  |

|                                  |                                             |                         | View synboli                                                      |                  |

| -                                |                                             |                         | Names                                                             |                  |

|                                  | Close                                       | B                       | Array Rows I Columns I                                            |                  |

|                                  | nouse                                       | L: mouseAddPt()         | Rotate Sideways Upside Down R: Rotate 90                          | <b></b>          |

|                                  |                                             | t location for the inst | notate Sitte Mays Upsitte Down                                    |                  |

|                                  |                                             | icfb -                  |                                                                   |                  |

|                                  |                                             | File To                 | Model name ani06N Help 1                                          |                  |

|                                  |                                             |                         | Model Type system Auser ssign library NOSU Analog Parts.          |                  |

|                                  |                                             | *VARNIN                 | Multiplier 1 library cdsDefTechLib in r node                      |                  |

|                                  |                                             | 3                       | Fingers 1                                                         |                  |

|                                  |                                             |                         |                                                                   | 1                |

| 0                                | i 🔼 🎒 🍋 i                                   | 2 2 2                   | icfb - Log: /home/usuario/CDS.log Virtuoso® Schematic Editing: pr | inte ob de reb   |

| ~                                | - un n n n n n n n n n n n n n n n n n n    | ~ > <                   | Library Manager: WorkArea: /home/usuario/NCSU                     | I Instance 10.32 |

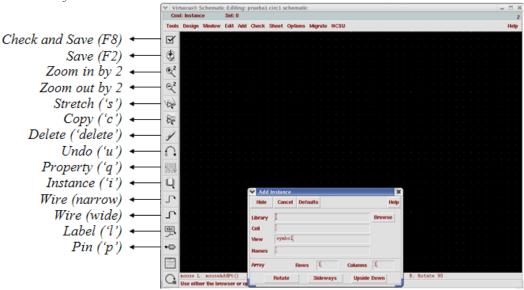

Figure 7. Adding instances in the schematic window.

- <u>*Wire components:*</u> select the **Wire (narrow)** icon, click to the first terminal and drag until the other terminal, then click again. In complex designs, for avoiding excessive wiring, labels can be employed. When two wire ends are labeled with the same name, they are effectively connected. Labels are created, e.g. with the **Label** icon or the short key 'l'.

- <u>Set instance properties</u>: you can modify at any time the properties of a certain component instance (resistance value, transistor dimensions, etc), e.g. by selecting the instance (click on it) and then clicking on the **Properties** icon, see Fig. 8. You can also change a group of instances of the same component simultaneously, by first selecting this group, then clicking in Properties and modifying the parameters, selecting **Apply to** > **All selected**. Most of the commands in Composer will start a mode (the default mode is selection), and as long as you do not choose a new mode (by clicking an icon, pressing a short key or selecting a menu item) you will remain in that mode. To quit from any mode and return to the default selection mode, the "*Esc*" key can be used.

| Edit 🚺             | Edit Object Properties      |                               | ×                   | Help                                                                                            |

|--------------------|-----------------------------|-------------------------------|---------------------|-------------------------------------------------------------------------------------------------|

| ow Cate            | OK Cancel Apply Defa        | aulte Dravious Novt           | Help                |                                                                                                 |

|                    | OK Cancer repry Den         |                               |                     | View                                                                                            |

| ary                | Apply To only curren        | it =   instance =             |                     |                                                                                                 |

| bal                |                             |                               |                     | a1 circ1 schematic Virtuoso® Analog Design Environment (1) =  Ready Tu27 C Simulator: spectre S |

| Layou<br>Analog    | Show system                 | 📕 user 📕 CDF                  |                     |                                                                                                 |

| Digita.<br>TechLil | Browse                      | Reset Instance Labels Display |                     | k Sheet Options Migrate NCSU Hel                                                                |

| TechLit            | Property                    | Value                         | Display             |                                                                                                 |

| TechLil            | Library Name                | CSU_Analog_Parts              | off =               |                                                                                                 |

| TechLit            | Cell Name P                 | nos4                          | off _               |                                                                                                 |

| TechLit<br>TechLit |                             | ymbolį                        | off -               |                                                                                                 |

| TechLit            |                             |                               |                     |                                                                                                 |

| :                  | Instance Name P             | <i>ŭ</i>                      | off -               | PP                                                                                              |

| fTechL:            |                             | Add Delete Modif              | v                   |                                                                                                 |

|                    | CDF Parameter               | Value                         | Diautau             |                                                                                                 |

|                    |                             | value<br>ani06P               | Display             | ₩ 151.85u                                                                                       |

|                    | Model name                  | aniusp                        | off 💷               |                                                                                                 |

|                    | Model Type                  | 🔶 system 🔷 user               | off                 | vdc=1.5 <u>VI</u> Vo                                                                            |

|                    | Multiplier                  | 1                             | off -               | gndt 🖕 o o o o 🚖 o o o o o o o o o o o o o o                                                    |

|                    | Fingers                     | 1                             | off 😐               |                                                                                                 |

|                    | Width (grid units)          | 1007                          | off =               | VI 400 VI VSS                                                                                   |

| sages —<br>filter  | Width                       | 151.05u M                     | off 🗕               |                                                                                                 |

| filter             | Width (minimum)             | 1.5u M                        | off _               | vdc=1.5 and                                                                                     |

| file is<br>ting li | Length (grid units)         | 8                             | off -               | Visa gadi S                                                                                     |

| ted lib<br>te of l | Length                      | 1.2u N                        | off -               |                                                                                                 |

| tion of<br>ted new |                             | 600n M                        | off _               | · · · · · · · · · · · · · · · · · · ·                                                           |

| coursew            | Length (minimum)            | 2.26575e-10                   | off _               |                                                                                                 |

|                    | Drain diffusion area        | 2.26575e-10                   |                     |                                                                                                 |

|                    | Source diffusion area       | -                             | off =               |                                                                                                 |

|                    | Drain diffusion perimeter   | 305.1u M                      | off                 |                                                                                                 |

|                    | Source diffusion perimeter  | 305.1u Mg                     | off _               |                                                                                                 |

|                    | Drain diffusion res squares | L                             | off -               | M: schHiMousePopUp() R: schHiObjectProperty()                                                   |

|                    | Source diffusion res square | s I.                          | off 🔤               |                                                                                                 |

|                    | Virtuoso-XL layout cell     | SU_TechLib_ami06 pmos         | off 💷               |                                                                                                 |

|                    | Drain diffusion length      | Į                             | off =               | Help 1                                                                                          |

|                    | <b>ँ</b>                    | r .                           |                     | n. Resetting                                                                                    |

| U                  |                             | 1                             |                     | d. Resetting to closest value.                                                                  |

|                    |                             |                               |                     |                                                                                                 |

|                    |                             |                               | cfb - Log: /home/us | suario/CDS.logVirtuoso® Schematic Editing: prueł [Graph Window 4] mié 03 de                     |

Figure 8. Property window of the transistor PMOS in the schematic.

There are basically two ways of creating schematics:

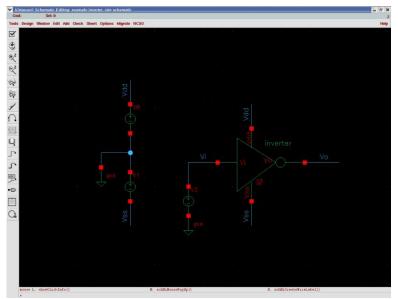

a) **Non-Hierarchical schematic**. Here, all the circuit is introduced in the schematic at the same (transistor) level, including the required sources. This is only viable for small designs, as depicted in Fig. 8.

b) Hierarchical schematic. If your design is very large, or if you want to reuse your design in other designs (e.g. an OpAmp to be employed in other circuits), you should create basic blocks at a low level, then create symbols for them and then use these symbols as basic components at a higher hierarchical level of the design. It is the same concept employed in SPICE netlists with the .SUBCKT command. When a certain circuit design consists of smaller hierarchical components (or modules), it is usually very beneficial to use this approach, first identifying such modules early in the design process and then assigning each such module a corresponding symbol (or icon) to represent that circuit module. This step largely simplifies the schematic representation of the overall system. The "symbol" view of a circuit module is an icon that stands for the collection of all components within the module. A symbol view of the circuit is also recommended for some of the subsequent simulation steps; thus, the schematic capture of the circuit topology is usually followed by the creation of a symbol to represent the entire circuit. The shape of the icon to be used for the symbol may suggest the function of the module (e.g. logic gates - AND, OR, NAND, NOR), but the default symbol icon is a simple rectangular box with input and output pins. Note that this icon can now be used as the building block of another module, and so on, allowing the circuit designer to create a system-level design consisting of multiple hierarchy levels.

This is the approach that will be followed in our example. To doing this, we have to create a symbol view of the inverter.

#### 5.2.2. Symbol Creation

a) First, you have to create pins in your schematic in those non-global nets (inputs, outputs, supplies perhaps) that have to be accessible outside the symbol. For doing this, you can select the **Create Pin** icon in the Composer schematic window, select the pin name, its input or output configuration, etc, and then click at the end of the wire when the pin has to be placed. Six pin icons have been placed in the example of Fig. 5: v+, v-, ibias, vdd, vss (input pins) and out (output pin).

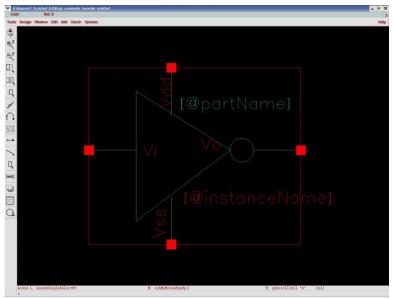

b) Now, select *Design > Create Cellview > From cellview*. A window appears that by default creates a symbol view from the schematic view. Just click OK. A black window pops up with the symbol. It can be edited if desired (changing shape, pin distribution, etc.). Fig. 9 shows the resulting symbol (after some editing) and the actions associated to the left icons. Now you can use your design in a higher hierarchical schematic. For instance, in a new schematic window, where the inverter symbol could be instantiated including sources to have it ready to be simulated, as shown in Fig. 10. Note: the sources have to be included in the higher hierarchical schematic, so as to have the circuit in the inverter without any ideal components.

We can go up and down in the hierarchy with menu options or with shortkeys 'X' (or 'x' for read-only mode) to descend and 'b' to ascend. Parameters for voltage and current sources are set as for any other component, by selecting the instance and editing its properties.

Figure 9. Symbol creation.

Figure 10. Instancing the created symbol in a new schematic.

#### 5.3. Simulation

After the transistor-level description of a circuit is completed using the Schematic Editor, the electrical performance and the functionality of the circuit must be verified using a Simulation tool. The detailed transistor-level simulation of your design will be the first in-depth validation of its operation, hence, it is extremely important to complete this step before proceeding with the subsequent design optimization steps. Based on simulation results, the designer usually modifies some of the device properties (such as transistor width-to-length ratio) in order to optimize the performance.

The initial simulation phase also serves to detect some of the design errors that may have been created during the schematic entry step. It is quite common to discover errors such as a missing connection or an unintended crossing of two signals in the schematic. Some of these errors (e.g. floating nodes) can be detected even before simulation, by pressing the *Check and Save* icon in the schematic window. The second simulation phase will follow the "extraction" of a mask layout (post-layout simulation), to accurately assess the electrical performance of the completed design. Like in other simulation environments, it is the netlist text file *extracted* from the schematic (or layout) what is actually simulated. In order to start simulations, from the Composer window that contains the schematic you want to simulate, choose *Tools > Analog Environment*. The simulation window appears (Fig. 11).

| Virtuoso® Analog Desi<br>Status: Ready | T=27 C Simulator: spectre                           | 3<br>Hele             | Circuit to be     |

|----------------------------------------|-----------------------------------------------------|-----------------------|-------------------|

| Session Setup Analyses<br>Design       | Variables Outputs Simulation Results Tools Analyses | ц<br>Ц                | → Choose design   |

| Library pruebal                        | # Type Arguments Enable                             | JAC<br>F TRAN<br>J DC | ← Choose analysis |

| Cell circ1<br>View schematic           | List of analysis to be performed                    | t t t<br>x y z        | Set variables     |

| Design Variables                       | Outputs                                             | <b>⊡</b> ∎∵́          | Choose outputs    |

| # Name Value                           | # Name/Signal/Expr Value Plot Save March            | 4                     | → Delete          |

| Dasim                                  |                                                     | 1                     | Run simulation    |

| Design<br>variables                    |                                                     | 8                     | Stop simulation   |

|                                        | Plotting mode: Replace =                            |                       | → Plot output     |

Figure 11. Analog Design Environment window.

By default, the design from which we have launched the window can be simulated using Spectre.

#### 5.3.1. Setting simulator

We can change the design with the corresponding icon or using the menus. We can also change the simulator by choosing *Setup->Simulator/Directory/Host* and setting, e.g. HSPICE. Obviously, the chosen simulator must be installed and licensed.

#### 5.3.2. Setting models

Also by default the component models for the library technology (in our example AMI  $0.5\mu$ ) will be used. If we want to use other models, we can store them in the directory of our choice and select *Setup>Model Path*, typing the full path (including filename) of the model(s) needed for simulation, before the path for the default models (list position means precedence in the search for models). This procedure assumes that your models have the same name as the default models. *5.3.3. Setting design variables*.

We can use in our schematic design variables for the component parameters, so that their values can be assigned just before simulation. For instance, we can name some (or all) of the transistor lengths as 'L'. Then, in the simulation window we assign the desired value to L. This way, we can make several simulations just changing the parameter(s) without having to edit the schematic. For editing design variables, choose *Variables >Edit* (or select the corresponding icon).

#### 5.3.4. Selecting the analysis

Several analyses can be performed (DC, AC, transient, etc.). For selecting the required analysis, choose *Analysis* > *Choose* (or the corresponding icon) and complete the settings in the window that appears. *Example: DC analysis (Fig. 12), choose 'dc', 'Select Component', choose the component in the schematic to be swept, choose the option 'dc', and specify the dc start and stop values to perform the analysis for.*

Currents cannot be plotted by default. If you are interested in viewing currents in your circuit, choose: *Output > Save all ....> Select all DC/transient terminal currents* (for DC and transient analyses) or *Select all AC terminal currents* (for AC analysis).

| ок    | Cancel                 | Defaults    | Apply      |                           |          |                  | Hel |

|-------|------------------------|-------------|------------|---------------------------|----------|------------------|-----|

| Analy | ````                   | · · ·       | ⇒ac<br>⇒xf | ⇔sp<br>⇔pss               | · ·      | sto 🔷 spss<br>se |     |

|       |                        |             |            | alysis                    |          |                  |     |

| Save  | DC Ope                 | rating Poir | n j        |                           |          |                  |     |

|       | ep Variab<br>Femperat  |             |            | Component                 | Name     | ∕VŬ              |     |

|       |                        | nt Parame   | eter       | Se                        | lect Cor | nponent          |     |

|       | vlodel Pa              | rameter     |            | Parameter                 | Name     | dď               |     |

| Swee  | ep Range               |             |            |                           |          |                  |     |

| · · · | Start-Sto<br>Center-Sj | ' St        | art -      | 1.5                       | Stop     | 1.5              |     |

|       | ep Type<br>inear       | -           |            | > Step Size<br>Total Poir |          | 1000             |     |

| Add S | Specific I             | Points 🗌    |            |                           | 163      |                  |     |

|       |                        |             |            |                           |          |                  |     |

#### Figure 12. DC analysis option.

#### 5.3.5. Running the simulation

When the former steps are performed, simulation can start. Click the Green Traffic Light Icon (bottom right corner of the simulation window) or choose Run > Simulation to run the simulation. If you want to interrupt the simulation at any instant, click the Red Traffic Light Icon or choose Run > Interrupt.

#### 5.3.6. Plotting the simulation results

There are different ways of plotting the results of a simulation. Here we are going to use the **Calculator** tool. After running the simulation, choose Tools > Calculator. A calculator window appears (see Fig. 13).

|             |          |            |           | onst Options H   |                   |            |   |

|-------------|----------|------------|-----------|------------------|-------------------|------------|---|

| home/       | usuario  | /simula    | tion/circ | 1/spectreS/schen | natic/psf         |            |   |

| Selectio    | n choice |            |           |                  |                   |            |   |

|             |          |            |           |                  |                   |            |   |

| <u>r</u> ci | p grapn  | selecti    | on        | tran ac dc       | swept_dc info no. | ise ni     |   |

| off O       | fami     | NO 1       | wave 🔿    | vdc 🔍 idc 🔾      |                   |            |   |

| 011 0       | Turin    | <b>y</b> 0 | wave O    | vac 🖲 iac 🖯      |                   |            |   |

|             |          |            |           |                  |                   |            |   |

| /DC("/\     | (i')     |            |           |                  |                   |            | - |

|             |          |            |           |                  |                   |            |   |

| Appen       | d 🔻      | 1          | 111       | 1/x              | b1f               | dBm        |   |

|             |          |            | -         | 10**X            | bandwidth         | delay      |   |

| Clear       | U        | ido 📊      | lot       | Rn               | clip              | deriv      |   |

|             |          |            |           | abs              | compression       | dft        |   |

| 1/x         | eex      | Clst       | Enter     | acos             | compressionVRI    | dftbb      |   |

| +           | 7        | 8          | 9         | acosh            | convolve          | evmQpsk    |   |

| +           |          | 0          | 9         | asin             | COS               | exp        |   |

| -           | 4        | 5          | 6         | asinh            | cosh              | eyeDiagram |   |

|             |          | -          |           | atan             | cross             | flip       |   |

| x           | 1        | 2          | 3         | atanh            | dB10              | fourEval   |   |

| 1           | 0        |            | +/-       | average          | dB20              | freq       |   |

|             |          | · · ·      |           |                  | 8888888           |            |   |

|             |          |            |           |                  |                   |            |   |

|             |          |            |           | Filter 📥 A       |                   |            |   |

Figure 13. Calculator.

With this tool we can, among other things:

- Plot in a waveform window the different currents and voltages

- Print (to a printer or a file) the selected waveforms

- Perform different functions on the selected waveform (multiply, divide, dB calculation, DFT, THD calculation, bandwidth, maximum and minimum calculation, etc).

- Use as a normal calculator for making calculations

You can select the **Help** option for details. When we want to display a certain waveform, we first select the button corresponding to the type of waveform. The most common are:

vt: nodal voltage (transient analysis)

it: terminal current (transient analysis)

vf: nodal voltage (AC analysis)

if: terminal current (AC analysis)

vs: nodal voltage (DC sweep)

is: terminal current (DC sweep)

vdc: nodal voltage (quiescent value)

idc: terminal current (quiescent value)

Then, we just click on the corresponding wire (voltages) or terminal (currents) in the schematic. Finally, we select in the calculator:

**Plot**: select the small '*plot*' icon, or select '*append*' on the left side of the calculator, to plot the waveform without removing already displayed waveforms.

**Clear**: To remove all the displayed waveforms.

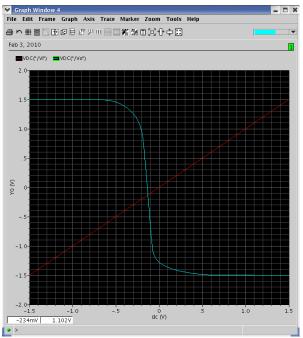

We can continue selecting circuit nodes and selecting the '*plot*' icon. Finally, press *Esc* for disabling the current action. The Waveform Window, showing the input and output voltages of the inverter, is shown in Fig. 14. Different configurations can be chosen (various graphs or axes, cursors, etc.). Press the **Help** button for details. If you want to modify and re-simulate your circuit, just change your schematic, design variables or simulation command, run again the simulation and select *Window* > *Update results* in the Waveform Window.

Figure 14. Plotting the results.

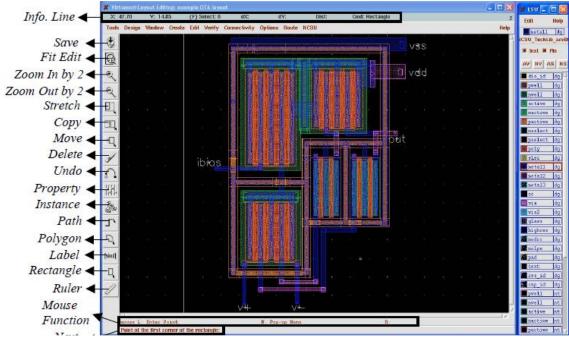

#### 5.4. Layout

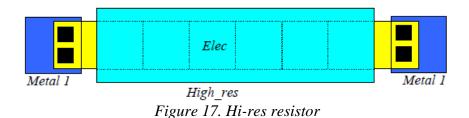

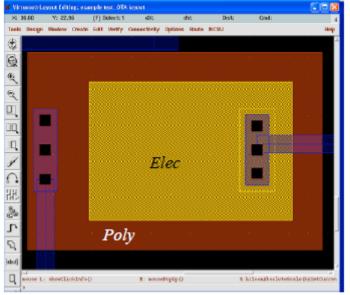

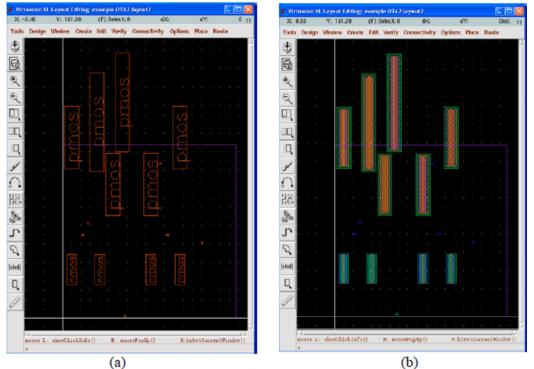

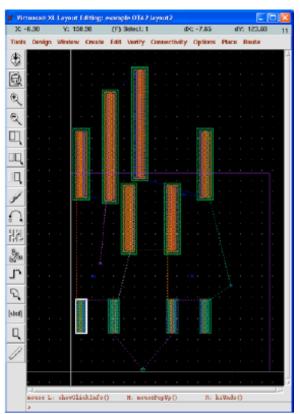

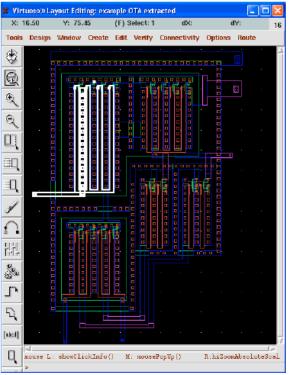

The creation of the mask layout is one of the most important steps in the full-custom (bottomup) design flow, where the designer describes the detailed geometry and the relative positioning of each mask layer to be used in actual fabrication, using a **Layout Editor**. Physical layout design is very tightly linked to overall circuit performance (area, speed and power dissipation) since the physical structure determines the transconductances of the transistors, the parasitic capacitances and resistances, and obviously, the silicon area that is used to realize a certain function.